With increased economic burdens, semiconductor manufacturing is facing formidable hurdles to keep on track with Moore's Law. There is no one solution for the next-generation factory but a number of them, which fab managers must select and modify to meet requirements.

Denis Fandel and Robert Wright, International Sematech Manufacturing Initiative, Austin, Texas -- Semiconductor International, 12/1/2009

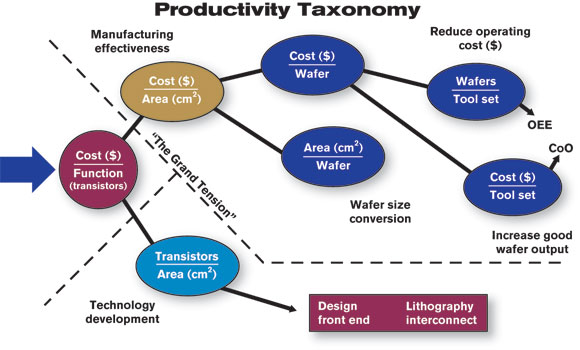

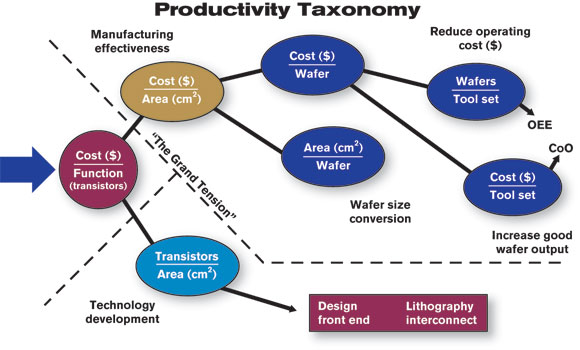

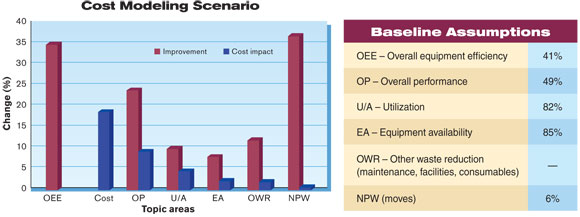

The International Sematech Manufacturing Initiative (ISMI) continues to be deeply involved in moving industry productivity forward by investigating next-generation fab infrastructure and capabilities. Part of this activity consists of analyses, through sophisticated simulation and modeling, of possible cycle time and cost savings based on improving overall equipment efficiency and factory operational performance (Fig. 1).

|

|

1. Part of the effort to increase productivity by investigating next-generation fab infrastructure and capabilities consists of analyses made using sophisticated simulation and modeling. |

Burdened by the current economic downturn, the industry is facing more formidable hurdles than ever in its efforts to keep abreast of Moore's Law. Much will depend on its ability to derive the maximum production improvements and efficiency from current and future fabs. However, the fragile state of the economy has impeded next-generation fab efforts. It is too early to determine how much this effect will last or how much it will delay the move toward next-gen fabs.

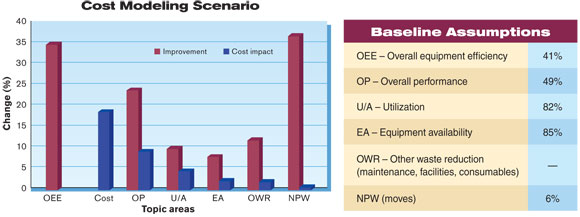

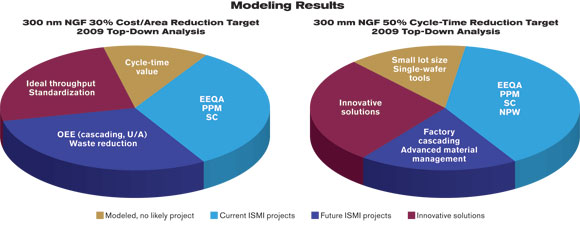

This change in the economic climate has forced a re-evaluation of exactly what is possible and when improvements in first wafer delay, set-up time, equipment availability, small lot manufacturing and single-wafer processing (SWP) for low- or high-mix business models might be ready for introduction. An important part of this will be determining how much equipment suppliers and chipmakers must participate and collaborate, although the exact arrangement will need to be resolved as we go forward. Extracting high-value cost leverage from the next-gen fab is going to be difficult, although combining initiatives such as factory operational performance (i.e., efficient cascading of lots) and equipment availability (i.e., predictive preventive maintenance) may provide considerable latitude and capability to improve cycle times (Fig. 2).

|

|

2. It will not be easy to get high-value cost leverage from next-gen fabs. Combining options such as the efficient cascading of lots with predictive preventive maintenance may result in considerable capability to improve cycle times in next-gen fabs. |

In short, current economic and cost pressures continue to overshadow R&D efforts, which require considerable reevaluation of what can be done in today's economic environment, particularly in terms of processing equipment. Investigations have shown that at least in the front end of line (FEOL), the physics required of the furnace batch equipment still in factories may be adequate for the wafer processing. For example, simulations to determine how cycle time improves with single-wafer processing have been done with two options: all or partial removal of batch tool operations from the fab and replacing them with SWP. Other issues also must be explored; these must be considered together with simulations in which wet bench batch tools are replaced with SWP tools and the cycle-time benefits examined. Of course, the cost to implement SWP will also require investigation.

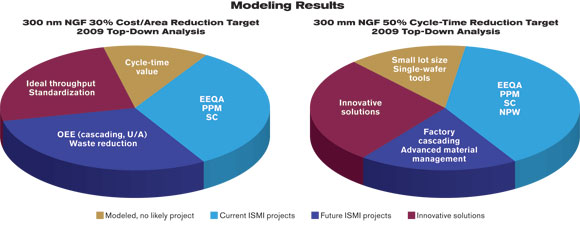

To attain this type of next-gen fab, ISMI has determined that considerable effort must be devoted to infrastructure. Here, through software or equipment improvements or alterations (or both), is where the evolution to the next-gen fab will take place. The transition will not be easy; significant design or redesign requirements will introduce high costs and implementation may take a long time. Implementation, of course, will be solely in new fabs, since any retrofit of older fabs would likely involve great effort and expense. Furthermore, the implementation cost of new types of software to drive equipment efficiencies and improved factory operational performance should not be overlooked (Fig. 3).

|

|

3. Significant design or redesign requirements will be costly and take time. These will take place in new fabs, since retrofitting older fabs would be extremelyexpensive. The cost of software to improve equipment efficiency and factory performance cannot be dismissed. |

Thus, the focus now appears to be mainly in eliminating waste across all wafer processes. This may require only small corrections here and there, avoiding the wholesale redesign of the fab and of the process equipment itself. This is an important part of the cost benefit study that must be done site-by-site and enterprise-by-enterprise to determine how to extract value out of these types of initiatives. This is no simple undertaking. For example, it is not like a 450 mm initiative, where the manufacturer is confronted by an entirely different dimension in which to work. Instead, manufacturers will continue to work with the same wafer diameter and labor to push equipment and factory performance to higher levels.

The power of simulation

Simulation experience indicates that with targeted changes in the model, a 40% reduction in cycle time might be possible for factories with 25-wafer lot sizes. Twelve-wafer lots were simulated to determine whether greater benefits in cycle time could be achieved. The results were promising: Cycle time was improved by slightly better than 50% when using single-wafer processing. More than just cycle time, however, the boundaries of fab operating performance must also be comprehended: How can the fab be run better? How can lots be cascaded for maximum efficiency?

Simulations were done in which cycle time was reduced by ~50% with a 12-wafer model when modeling multiple equipment and factory operational improvements compared with a 25-wafer factory. In both scenarios, significant improvements in cycle time were observed for both 25- and 12-wafer fabs in terms of optimized cascading of lots modeled as a single factor. Hence, both 25- and 12-wafer operations offer good opportunities for cycle-time reduction. Some fabs have a business model that would be more adaptable to smaller volumes, in this case 12-wafer lots, while others with much higher volumes can do better with 25-wafer lots.

Fab cycle-time reduction

From some dynamic factory simulations, greater challenges to reduce cycle times in the fab — from an equipment perspective — appear to be in equipment availability, improving that availability, and the reliability of the tools themselves. A side issue is that preventive maintenance should be made more predictive. When all these factors are simulated and we factor in predictive preventive maintenance, thereby reducing variability of downtimes, the benefits (or impact) of better cycle times for the fab or running more wafer starts per month that lower the cost per wafer become evident. Therefore, many factors that are needed for cycle-time improvement appear to lie on the equipment side of the equation. Unquestionably, fab processing equipment needs to be improved; however, the enabling costs could be considerable. Trying to push cycle time to lower values may require some capital investment, either in terms of more equipment or different equipment configurations.

The question of what would be a more cost-effective solution naturally arises: pushing utilization higher or the absolute run rates themselves. The simulations seem to suggest that rather than pushing cycle time to its maximum potential or capability, a more effective measure might be pushing cost benefits a bit higher. Questions such as how the fab's operations work, how good overall equipment efficiency is, and how this all is being executed in the fab become of great importance in terms of getting a favorable cost equation. In any case, understanding the problem one is trying to solve is of paramount importance; for this, one really needs to understand what the data is saying and how to visualize the data in terms of corrective actions that are necessary. To reset the bar higher requires a significant amount of upfront work.

Solving the cycle problems

Over the past two years, the industry has experienced an extremely challenging economic environment that has affected equipment, silicon and chip suppliers. Everyone, at all levels of the industry, has taken a hit and is still in recovery. We need to work as a team collaborating on this effort. This is the only way in which the industry will prosper and succeed. Specifically, as we look toward the future and we see signs of recovery, we also see additional 300 mm fabs that will be needed to satisfy the demand expected four or five years from now. To attain the productivity needed to stay on track with Moore's Law and continue to stimulate demand, while keeping costs down, the industry must continue to focus on next-generation factories and to leverage as much from joint R&D to realize these near-future goals.

The industry cannot wait another four or five years, expecting these problems to resolve themselves. Within the next 18 months to two years, we need to not only continue traditional improvement programs but start new initiatives in our factories to contain costs and increase productivity, thereby creating a better business environment.

ISMI's member companies, chipmakers and industry have made great strides in reducing cycle times through various improvement programs; however, some fabs can be substantially improved. Our factory simulation programs have clearly shown this. Assuming equipment availability and reliability can be improved, relying on existing business models appears to be a good idea. If you want to go to a smaller lot size, SWP will provide significant leverage for cycle-time improvement. If you remain with 25-wafer lots, because of the higher volume, then maybe cycle time is not as important as cost.

At this point, one size does not fit all. The industry needs to work within itself to satisfy all its constituents — whether they are high-volume/low-mix or low-mix/high-volume or any combination thereof — to find an overall solution. All aspects of the industry can improve their productivity and gain cost benefits that can be passed on to the customer. There is no one solution for the next-gen factory, but a number of them, which fab managers must select and modify to meet their own particular requirements.

| Author Information |

| Denis M. Fandel manages the economic modeling and analysis activities atInternational Sematech Manufacturing Initiative(ISMI). He previously worked in the IBM semiconductor strategic planning arena in a variety of management and staff positions within the marketing, manufacturing and financial disciplines. Fandel received a B.S. in mathematics from the University of Wisconsin. Email:denis.fandel@sematech.org |

| Robert L. Wright manages discrete event simulation activities at ISMI and has 13 years of experience in both dynamic simulation and static cost modeling. He received a B.B.A. in management and an M.S. in technology from Texas State University. Email:robert.wright@sematech.org |