At IEDM, Intel manager Paul Packan said Intel's flagship 32 nm technology achieved record drive current levels, with the PMOS transistor showing a 35% drive current improvement over the 45 nm PMOS device. "For the first time, linear drive currents on the PMOS have overtaken NMOS," he said. The sharp gain in PMOS performance comes partly by adding germanium to the SiGe stressors, and from the replacement-gate process.

David Lammers, News Editor -- Semiconductor International, 12/10/2009

Intel Corp. presented details on its 32 nm logic technology at the International Electron Devices Meeting (IEDM), reporting that its fourth-generation strain techniques have boosted the PMOS performance to a historic point. "For the first time, linear drive currents on the PMOS have overtaken NMOS," said Paul Packan, 32 and 15 nm technology programs manager.

For the oft-quoted saturated drive current, the 32 nm NMOS value remains higher, at 1.62 mA/μm Idsat compared with 1.37 mA/μm for the 32 nm PMOS transistor. Packan said the PMOS linear drive current (ldlin) reached 0.24 mA/μm, a 35% improvement over the 45 nm PMOS transistor. The NMOS device Idlin gained a 20% improvement, partly from a raised source-drain architecture, reaching a linear drive current of 0.231 mA/μm. Linear drive current is important because transistors rarely get to full saturation, making Idlin a meaningful metric for real-world device operation.

|

|

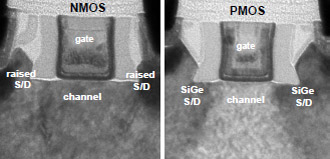

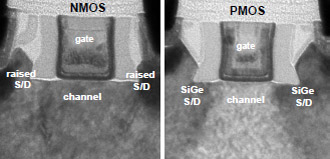

Intel used a raised source-drain for its 32 nm NMOS transistors. |

With NMOS and PMOS now in rough parity, designers can adjust the size of the PMOS transistors to their needs, said Mark Bohr, a senior fellow at Intel. "For many generations, there was a 2:1 ratio between the NMOS and PMOS," largely caused by inherently different mobilities between electrons and holes. "At the 32 nm generation, our saturation and linear drive currents are closer to being matched; we are getting very close." That means for the Westmere processor Intel designers could create circuits with smaller PMOS transistors in some cases, Bohr said.

The sharp gain in PMOS performance comes partly by adding more germanium to the SiGe stressors, to a 40% level. Also, "we are moving the SiGe closer to the channel at the 32 nm generation, which is challenging at these dimensions," Bohr said.

The replacement gate technique adds another boost, rivaling that of the SiGe stressors. Before high-k/metal gate technology was introduced, the polysilicon electrode was neutral in terms of strain on the PMOS channel. With the replacement gate, or gate-last, technology, removal of the sacrificial gate allows the SiGe stress regions to exert a stronger tensile strain on the channel, reaching 2 GPa.

For the NMOS, the raised source and drain reduces resistance, "helping to mitigate the pitch scaling issues," Packan said. By moving transistors closer together, there is less room for stress regions. Though in previous interviews Bohr has not been positive about the value of SiC stressors on the NMOS channel, he declined to comment on whether Intel is using SiC at the 32 nm node.

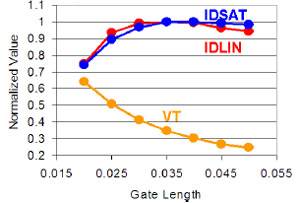

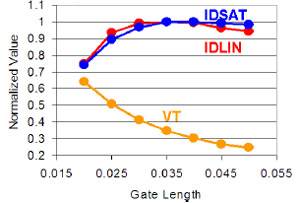

Although Intel remains on a Moore's Law pace in terms of contacted gate pitch scaling, with a 112.5 nm pitch, shrinking is no longer delivering the speed improvements seen in past generations, Packan said. With smaller dimensions, less material can be deposited to add strain. And threshold voltages have crept up slightly in recent years at the same Ioff levels.

|

|

Without increased strain, CMOS transistors would be losing performance as the gate length scales. |

"Traditional scaling is losing steam," Packan told the standing-room-only Wednesday IEDM session on leading-edge CMOS. He estimated that were it not for the additional benefits of higher strain, performance actually would have declined for the 32 nm transistors. One reason, Bohr said, is that to counter short channel effects in the aggressively scaled gates the channel must receive higher dopant levels, causing threshold voltages to rise and slowing down the transistor.

"We need a new paradigm for performance improvement," Packan said.

Though several participants at IEDM said CMOS scaling is likely to slow to a three-year pace, Bohr said Intel plans to stay on a two-year cadence. The Westmere processors are shipping now from two Intel fabs to computer vendors, and the 22 nm technology is on pace to ship two years later. Not only does Intel want to remain ahead of its MPU competition, its computer customers need faster MPUs every two years so they can sell new systems to their customers, he said.