Vertical gate-all-around (GAA) devices are considered as important promising candidates to replace FinFETs at and beyond the 2nm technology node. However, the fabrication of vertical GAA field-effect transistors (FETs) faces serious challenges for improving their performance and manufacturability. In IEDM 2018, Dr. Ryckaert1 from IMEC emphasized that the length of the gates and the alignment of the gate to the channel were key challenges for the research and fabrication of vertical GAA devices.

Fortunately, Professor Huilong Zhu started a research project in 2016 to investigate these issues in his research group. A new type of vertical nanowire (NW)/nanosheet (NS) FETs, called Vertical Sandwich Gate-All-Around FETs or VSAFETs in short,was presented and fabricated in Zhu’s Group to overcome the shortcomings of existing vertical devices. The results have been published recently on IEEE Electron Device Letters (DOI: 10.1109/LED.2019.2954537).

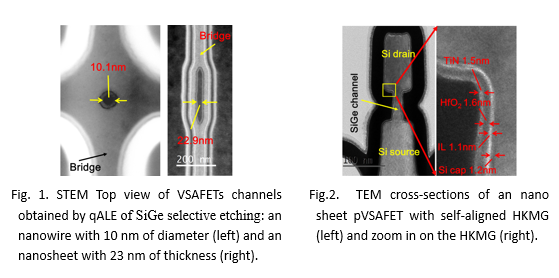

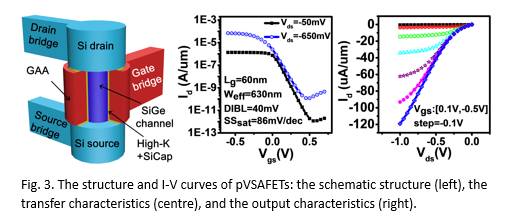

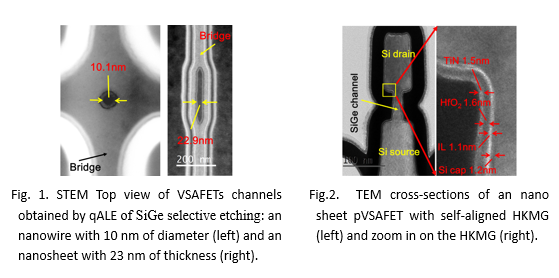

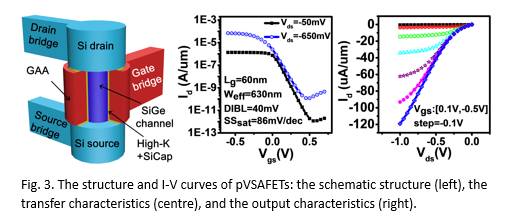

In some detail, an isotropic quasi-atomic-layer-etching (qALE) of SiGe selective etching was investigated systematically and applied to fabricate NW/NS channels in epitaxial growth Si/SiGe/Si structures. The precise control of both the channel size and gate length can be achieved by the qALE and the epitaxial growth. Self-aligned HKMG for vertical GAA FETs was obtained for the first time. Importantly, the integration flow for the VSAFETs is compatible with that for state-of-the-art complementary metal-oxide-semiconductor (CMOS) technology. The pVSAFET with a gate-length/NS-thickness of 60 nm/20 nm was obtained. The SS, DIBL, and Ion/Ioff ratio of the device were 86 mV/dec, 40mV and 1.8?105, respectively.

This work was partially supported by the Academy of Integrated Circuit Innovation of Chinese Academy of Sciences (No. Y7YC01X001).

References:

1. J. Ryckaert, "3D integration for density and functionality," in 2018 IEEE International Electron Devices Meeting (IEDM), short course. San Francisco, USA, 2018.