Recently, the International Electron Devices Meeting (IEDM) 2020 was held in the form of video conference. Prof. Ming Liu’s team from IMECAS presented the latest research results of compact modeling for independent dual-gate amorphous IGZO thin film transistor (IDG a-IGZO TFT).

On account of the extremely low leakage current and the possibility of low-temperature fabrication, a-IGZO TFT is under active research and development in the circuit application such as flexible display, memory and 3D integration. Especially the IDG a-IGZO TFT has become the key choice in the industry due to its controllability of turn-on voltage and enhancement of on/off-current ratio. To further effectively evaluate circuit performance, it is significant to have an accurate compact model describing the physical device behavior. However, due to the amorphous disordered structure, charge transport in a-IGZO exhibits complex behavior, which also brings difficulty in calculating the surface potentials, the latter is the key issue in the modeling of IDG transistors. To our understanding, the surface potential based completely compact model of IDG a-IGZO TFT considering amorphous structure and charge transport is still lacking.

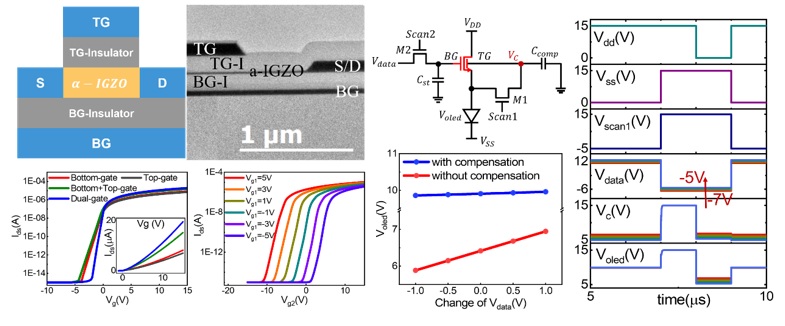

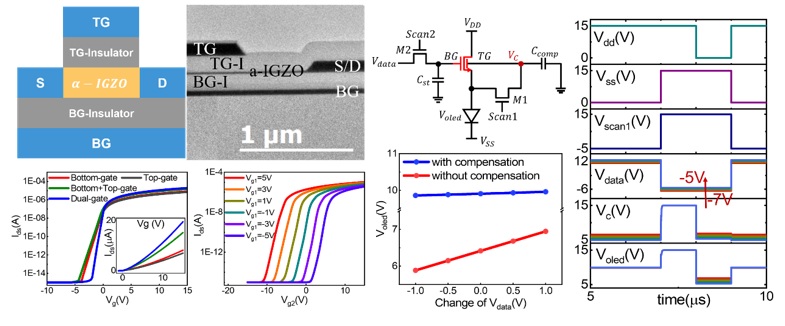

In response to the above questions,Prof. Ming Liu’s team develop a physics-based compact model for IDG a-IGZO TFT considering both traps and free electrons in an analytical way. With the combination of percolation conduction, trap-limited conduction, variable range hopping for transport mechanism and a new capacitance calculation method for dual-gate transistors, the model accurately replicates the experimental data. Also, the compact model is evaluated for circuit design in SPICE.

The paper “A New Surface Potential Based Compact Model for Independent Dual Gate a-IGZO TFT: Experimental Verification and Circuit Demonstration” was accepted by IEDM 2020. The first author Jingrui Guo, a master student from IMECAS, gave an oral report online. This article belongs to the top ranked student papers of IEDM 2020, and it is planned to be included in the special issue of IEEE Transactions on Electron Devices.

Fig 1. The advantages of IDG a-IGZO TFT with high driving current and threshold voltage are simulated based on the model, and the compensation function of threshold voltage is realized in AMOLED pixel circuit.(Image by GUO’s group)

Contact:

Associate Researcher GUO Jingrui

Key Laboratory of Microelectronic Devices Integrated Technology, CAS

E-mail:guojingrui@ime.ac.cn